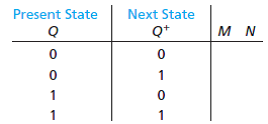

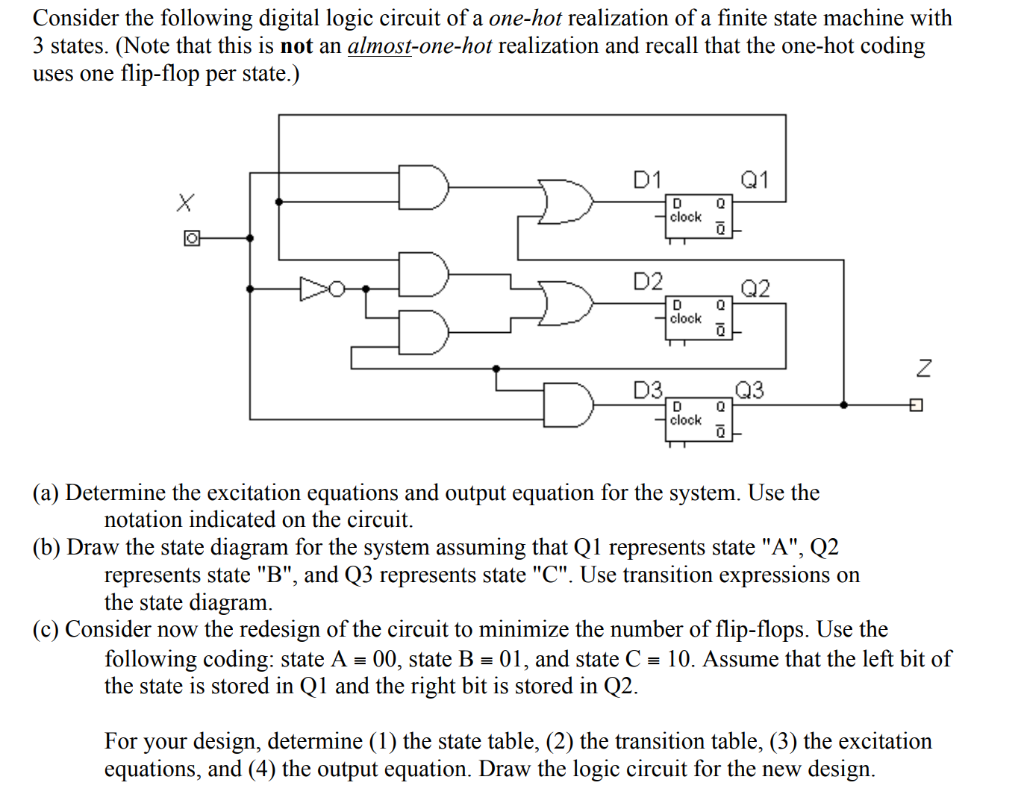

COE 561 Digital System Design & Synthesis Sequential Logic Synthesis Dr. Aiman H. El-Maleh Computer Engineering Department King Fahd University of Petroleum. - ppt download

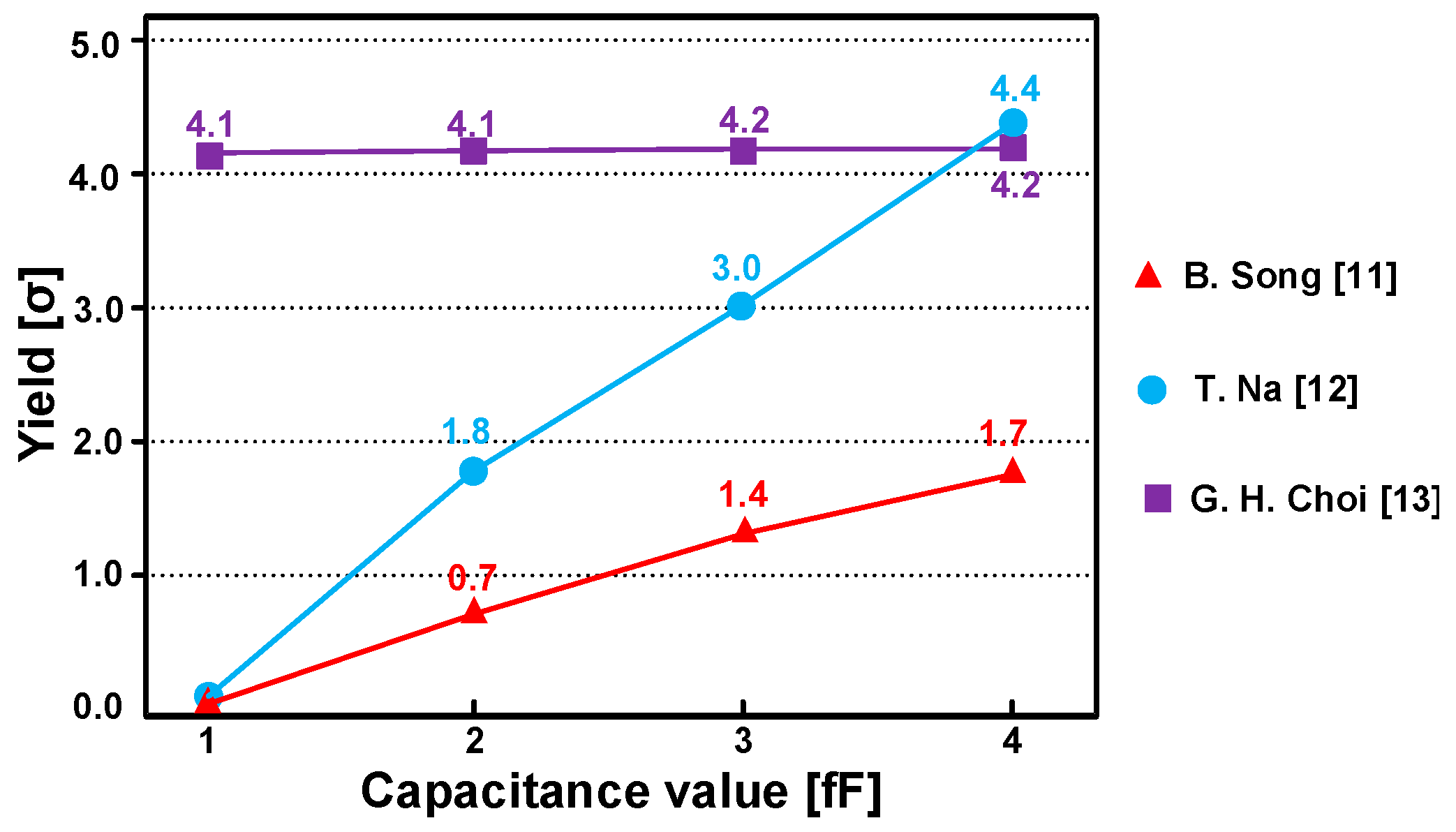

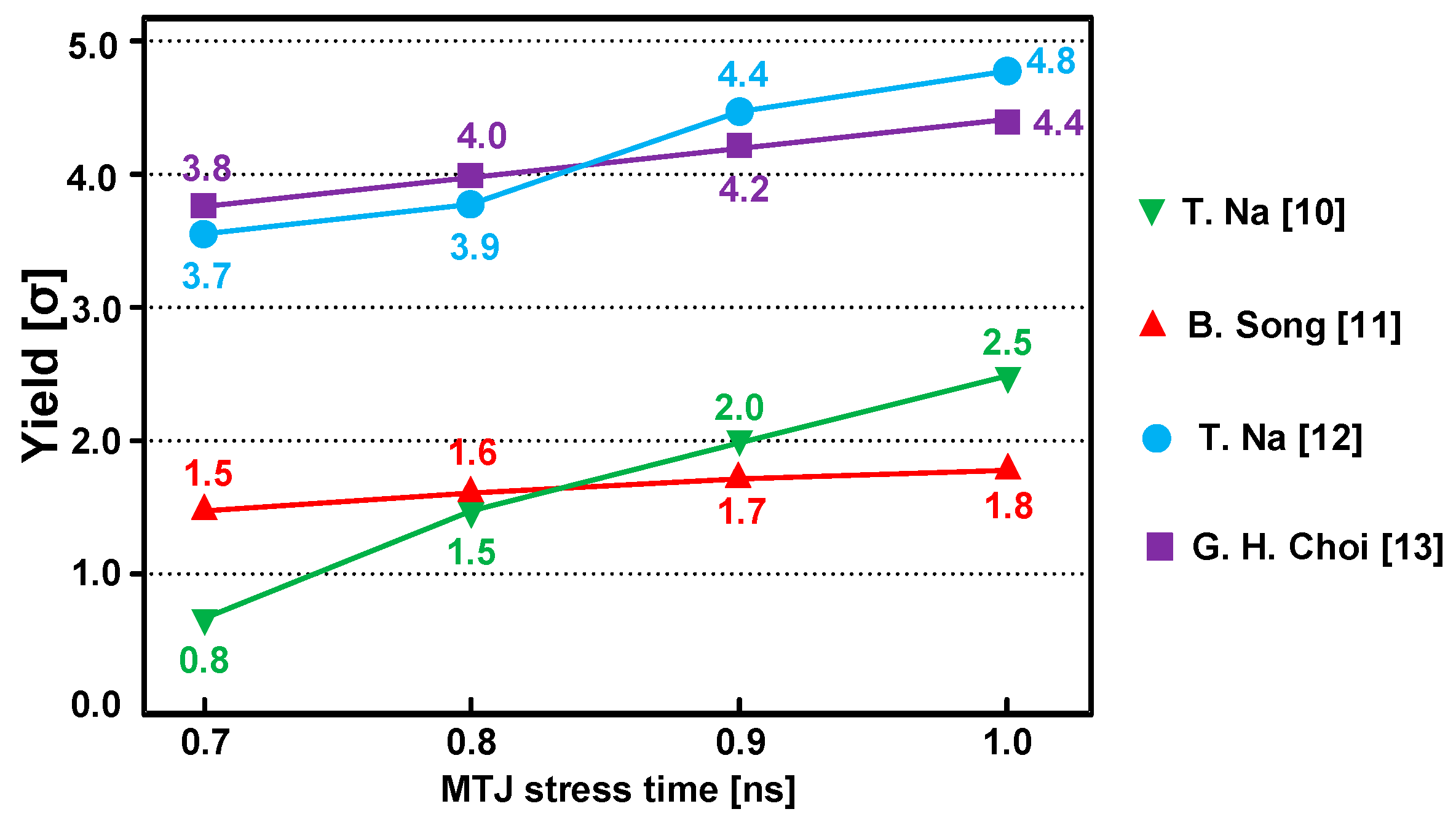

Electronics | Free Full-Text | Analysis of State-of-the-Art Spin-Transfer-Torque Nonvolatile Flip-Flops Considering Restore Yield in the Near/Sub-Threshold Voltage Region | HTML

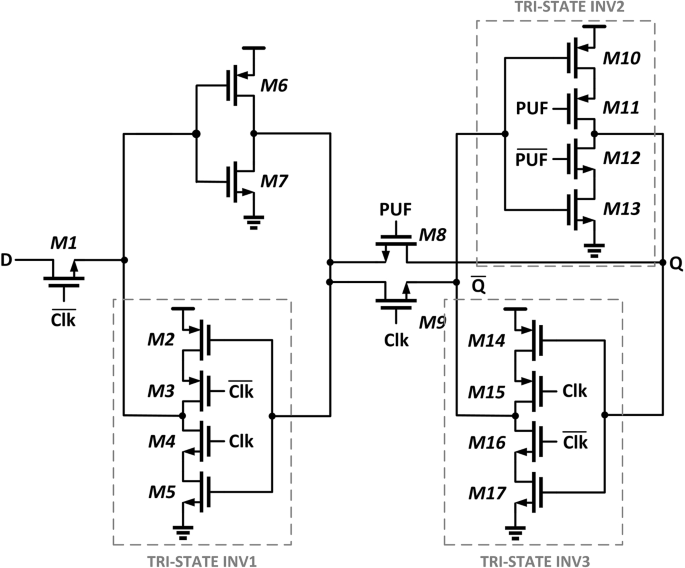

Utilizing manufacturing variations to design a tri-state flip-flop PUF for IoT security applications | SpringerLink

Electronics | Free Full-Text | Analysis of State-of-the-Art Spin-Transfer-Torque Nonvolatile Flip-Flops Considering Restore Yield in the Near/Sub-Threshold Voltage Region | HTML